JPRS L/9703 30 April 1981

# **USSR** Report

CYBERNETICS, COMPUTERS AND AUTOMATION TECHNOLOGY

(FOUO 13/81)

#### NOTE

JPRS publications contain information primarily from foreign newspapers, periodicals and books, but also from news agency transmissions and broadcasts. Materials from foreign-language sources are translated; those from English-language sources are transcribed or reprinted, with the original phrasing and other characteristics retained.

Headlines, editorial reports, and material enclosed in brackets [] are supplied by JPRS. Processing indicators such as [Text] or [Excerpt] in the first line of each item, or following the last line of a brief, indicate how the original information was processed. Where no processing indicator is given, the information was summarized or extracted.

Unfamiliar names rendered phonetically or transliterated are enclosed in parentheses. Words or names preceded by a question mark and enclosed in parentheses were not clear in the original but have been supplied as appropriate in context. Other unattributed parenthetical notes within the body of an item originate with the source. Times within items are as given by source.

The contents of this publication in no way represent the policies, views or attitudes of the U.S. Government.

COPYRIGHT LAWS AND REGULATIONS GOVERNING OWNERSHIP OF MATERIALS REPRODUCED HEREIN REQUIRE THAT DISSEMINATION OF THIS PUBLICATION BE RESTRICTED FOR OFFICIAL USE ONLY.

JPRS L/9703 30 April 1981

# USSR REPORT CYBERNETICS, COMPUTERS AND AUTOMATION TECHNOLOGY (FOUO 13/81)

# CONTENTS

| C.  | FΝ | Œ    | PΔ     | Т |

|-----|----|------|--------|---|

| UT. | Ľ  | 1157 | $\sim$ |   |

|          | of Presidium of USSR Supreme Soviet,                                                                            |    |

|----------|-----------------------------------------------------------------------------------------------------------------|----|

|          | Comrade Leonid Il'ich Brezhnev                                                                                  | 1  |

|          | Instrument Building for the 26th CPSU Congress                                                                  | 3  |

|          | Some Problems of Science in Development of Control Systems                                                      | 11 |

|          | Toward New Positions of Automation of Control in Basic Sectors of Industry                                      | 20 |

|          | Problems Orientation of Computer Complexes of the International Small Computer                                  | 21 |

|          | The International Small Computer SystemStatus and Prospects for Development                                     | 33 |

|          | Present Status of the Problem of Tesigning Data Flow Computers With Non-Traditional Structures and Architecture | 47 |

|          | Task Orientation of Computer Systems by Means of Associative Learning                                           | 74 |

|          | Abstracts From the Journal 'MICROELECTRONICS'                                                                   | 75 |

| [!ARDWA! | RE .                                                                                                            |    |

|          | Systems Based on El'brus Family of Computing Machines                                                           | 78 |

|          | The M-10 Computer System                                                                                        | 94 |

- a - [III - USSR - 21C S&T FOUO]

|     | Microcomputers Based on n-Channel Metal Oxide Semiconductor Large-Scale Integrated Circuits (MOS LSIC's) Described                          | 100 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------|-----|

|     | Microelectronic Analog Processor for Matrix Reading of Images                                                                               | 109 |

|     | Basic Characteristics of YeS System Magnetic Disk Storage Units                                                                             | 118 |

|     | Organizational Analysis of Common Computer Resources in Homogeneous Multiprocessor Computer Systems                                         | 120 |

| SOF | TWARE                                                                                                                                       |     |

|     | Problems of Developing Automated Design Systems                                                                                             | 121 |

|     | Programming Fundamentals for the Unified Computer System                                                                                    | 130 |

|     | Software for M-400 Minicomputer of VTsKP of Uzbek Academy of Sciences                                                                       | 138 |

|     | Principal Directions of Development and Standardization of Languages and Packages of Applied Programs for Automated Process Control Systems | 140 |

| APP | PLICATIONS                                                                                                                                  |     |

|     | Prospects for Development of Automated Control Systems                                                                                      | 149 |

|     | The Principles of Designing Collective-Use Functionally Distributed Systems                                                                 | 15  |

|     | Application of Microprocessors in Instrument Building                                                                                       | 16: |

| NET | TWORKS                                                                                                                                      |     |

|     | Architecture of Computer Networks                                                                                                           | 17  |

|     | Computer Network Analysis and Synthesis Methods                                                                                             | 18  |

|     | Structure, Function of Branch Computer Network Introduced                                                                                   | 18  |

|     | New Book on Computers and Computer Networks                                                                                                 | 18  |

|     | Basic Telegraph, Telephone Units in Computing Systems Reviewed                                                                              | 19  |

|     | Basic Characteristics of YeS Remote Data Transmission System                                                                                | 20  |

- b -

# FOR OFFICIAL USE ONLY

# PUBLICATIONS

| New Book on Automating Control of Production Processes           | 216  |

|------------------------------------------------------------------|------|

| Equipment of Collective-Use Data Processing System Reviewed      | 220  |

| Control Systems for Data Banks and Bases Reviewed                | 227  |

| Specifications of Microprocessors Listed                         | 234  |

| Microprocessors Used in Control Systems for Industrial Processes | 237  |

| ASVI-M and SM Minicomputer Specifications                        | 2/12 |

- c -

**GENERAL**

LETTER TO GENERAL SECRETARY OF CPSU CENTRAL COMMITTEE, CHAIRMAN OF PRESIDIUM OF USSR SUPREME SOVIET, COMRADE LEONID IL'ICH BREZHNEV

Moscow PRIBORY I SISTEMY UPRAVLENIYA in Russian No 2, Feb 81 p 2

[Letter to general secretary of CPSU Central Committee, chariman of Presidium of USSR Supreme Soviet, Comrade Leonid Il'ich Brezhnev from Ministry of Instrument Making, Means of Automation and Control Systems]

[Text] Dear Leonid Il'ich! We are glad to report to you that, fulfilling the decisions of the 25th CPSU Congress and your instructions on economic problems and being guided by the decree of the CPSU Central Committee "On the socialist competition to meet the 26th CPSU Congress with honor," the workers, scientists, engineering and technical personnel and employees of the Ministry of Instrument Making, Means of Automation and Control Systems completed fulfillment of the plan of the 10th Five-Year Plan ahead of schedule by rates of growth in the volume of production. The volume of production of instruments, equipment, means of automation, computer equipment and other products of instrument building increased 1.7-fold during the five-year plan. Labor productivity during the five-year plan as a whole will increase by more than 52 percent, which exceeds the task of the five-year plan. The cost of produced products will decrease by more than 10 percent. The tasks of the five-year plan for production of the most important nomenclature and national consumer goods are also being fulfilled ahead of schedule.

The high work indicators of the sector are the result of extensive use of the advances of scientific and technical progress, development and introduction of modern equipment into production, of leading methods of labor organization and progressive technology and of improving the economic mechanism and economic methods of management. More than 2,500 of the most important types of instruments, means of automation, computer equipment and national consumer goods were produced during the five-year plan; more than 1,500 automated control systems, including 350 ASU [Automated control system] for production processes in the leading sectors of the national economy, were put into operation. The volume of output of articles using microelectronic equipment--integrated circuits, microprocessors and microcomputers --increased more than threefold and exceeded two billion rubles in 1980. In this case the main operating characteristics of the instruments and facilities of computer equipment--accuracy, speed and reliability--were improved significantly. Of the total volume of products produced, approximately half comprise articles assimilated during the 10th Five-Year Plan. A program is being realized to organize and develop production of numerical program control devices for metalworking equipment and robot manipulators and instruments for scientific research, agriculture and environmental monitoring.

1

Approximately 50 percent of the collectives of sector enterprises reported on fulfilling the tasks of the 10th Five-Year Plan ahead of schedule. Among them are the Moscow PO [Production Association] Manometr, the PO Leningrad Electrical Engineering Plant, the Kiev PO Kochelectropribor, the Orel PO Prompribor, the Moscow NPO [Scientific Production Association] Spektr, the Kishinev NPO Valna, the Minsk Clock Plant imeni 60-letiya of the Belorussian Communist Party and others.

The workers, scientists, engineering and technical personnel and employees of the sector, realizing the tasks advanced by the party at the October (1980) Plenary Session of the CPSU Central Committee, are laboring to fulfill the new increased socialist pledges in honor of the 26th CPSU Congress. Instruments, equipment, means of automation and computer equipment worth no less than 310 million rubles and national consumer goods worth 117 million rubles will be produced above the five-year task prior to the end of the current year. A number of investigations important to the national economy will be fulfilled ahead of schedule by the opening of the Party Congress including the fact that state trials will be completed and industrial production of highly productive computers for geophysical computer complexes for processing the data of geological oil and gas prospecting work will be begun. National consumer goods worth no less than 10 million rubles will be manufactured above the plan for two months of 1981.

The instrument builders assure the CPSU Central Committee and you personally, Leonid Il'ich, that they will struggle persistently to increase production efficiency and work quality, to fulfill the plans of the party in building of communism and will welcome the 26th Party Congress with honor. (27 November 1980)

COPYRIGHT: Izdatel'stvo "Mashinostroyeniye". "Pribory i sistemy upravleniya", 1981 [122-6521]

6521

cso: 1863

INSTRUMENT BUILDING FOR THE 26th CPSU CONGRESS

Moscow PRIBORY I SISTEMY UPRAVLENIYA in Russian No 2, Feb 81 pp 2-5

[Article by Doctor of Technical Sciences M. S. Shkabardnya, USSR minister of instrument building, means of automation and control systems]

[Text] Implementation of the course planned by the 25th CPSU Congress to increase production efficiency and product quality and acceleration of scientific and technical progress are related to harmonious development of the entire national economy of our country. Reducing the fraction of manual labor, support of complex mechanization and automation and improving methods and means of management are conditions for increasing material production efficiency. Solution of these most important problems posed by the party makes no sense without modern development of instrument building, computer technology and electronics. It is the given complex of sectors on the eve of the 10th Five-Year Plan that was identified by Comrade L. I. Brezhnev as the "catalyst of technical progress" and as the tasks of the five-year plan that provided for their leading development.

The instrument builders successfully completed fulfillment of the tasks of the 10th Five-Year Plan ahead of schedule. The selfless labor of our workers, engineers and scientists brings visible fruits. The extensive qualitative progressive changes in the structure of production, technical level and organization of the instrument building industry are the results of this labor.

Instrument building during the 10th Five-Year Plan compared to the previous period was developed more intensively and is characterized by a significant expansion of the nomenclature of instruments and means of automation according to the growth of the needs of the national economy, especially such leading sectors as power engineering, chemistry, nonferrous and ferrous metallurgy, machine building and so on, according to an increase of their technical level, accuracy and reliability, to an expansion of functional capabilities and to an increase of production volume.

The results of fulfilling the state plan and socialist pledges for 1976-1980 indicate that the collectives of the enterprises and organizations of Minpribor [Ministry of Instrument Making, Means of Automation and Control Systems of the USSR] coped successfully with the tasks posed to them.

The growth of production volume was 171.3 percent compared to 167.1 percent provided by the five-year plan, with an average annual growth rate of 11.35 percent (10.8 percent according to the plan) and labor productivity increased 1.52 times. More

3

than 70 percent of the growth of product output was achieved as the result of an increase of labor productivity. More than 2,500 new articles were developed and assimilated and more than 1,500 obsolete articles were taken out of production. Approximately 40 percent of the total product volume of the sector was produced with the state Emblem of Quality. As in previous years, production of means of control computer equipment, output of which increased 1.8-fold in 1980 compared to 1975, developed at the fastest rates. The production of instruments for monitoring and regulation of production processes and also of electric measuring instruments increased 1.8-fold, that of instruments for measuring mechanical values and weight-measuring and weight-proportioning devices increased 1.7-fold and that of instruments for scientific research increased 1.75-fold.

Much has also been done by instrument builders in developing the production of consumer goods: clocks, fountain pens, typewriters, jewelry, games, stationery and writing implements. The sector is now manufacturing several thousand types of these articles and approximately 80 percent of them have been renewed or newly assimilated, while the volume of their output increased 1.5-fold during the five-year plan.

Based on the systems approach, formulated during previous years, to establishment and development of production and complex use of devices and means of automation of different designation in the national economy, the technical policy of the sector oriented toward increasing the efficiency and expansion of utilization of modern methods and means of measurement, monitoring, automatic control and information processing, is being formulated and implemented in the form of a number of large purposeful programs.

They include a complex program of work to establish and organize production of an international small computer system—SM EVM, carried out by enterprises of Minpribor jointly with a number of enterprises of the socialist countries. More than 200 new devices of this unit system of computer equipment with developed peripheral equipment and software has been developed and assimilated. The enterprises of the sector have organized large-serial production of control computer complexes (UVK) of the new generation of SM EVM designed for automated production control systems, scientific experiment management systems and automated design control systems. At the same time, the laboriousness of producing most models of the SM EVM has been reduced more than one-half compared to previously produced machines, which made it possible to increase significantly the output of UVK of SM EVM in 1980. The serial output in various configurations and in the form of problem-oriented computer complexes creates a strong scientific and technical base for extensive use of computer equipment in this class for automation of production and labor processes of the most diverse nature in all sectors of the national economy.

An extensive program of work is being implemented to develop new seismic prospecting equipment and specialized computer complexes for processing geophysical information, the use of which will make it possible to increase significantly the efficiency of geological prospecting for oil and gas and also to evaluate and analyze the status of natural resources on large scales. New field digital seismic prospecting stations Progress have been developed and put into production and multiprocessor geophysical expedition computer complexes PS-2000 and other equipment have been developed within the framework of this program.

The production of devices and systems for numerical program control (ChPU) of metal-cutting machines and industrial manipulator robots, including those on a modern

1

microelectronic component base with built-in microprocessors and microcomputers, is being developed at high rates. Production of ChPU devices of different designation increased 2.6-fold during the 10th Five-Year Plan and models of them were completely renovated. More than 65 percent of the ChPU devices are being produced with the state Emblem of Quality. The decree of the CPSU Central Committee and the USSR Council of Ministers adopted at the beginning of 1980 "On a significant increase of the technical level and competitiveness of metal working, casting and woodworking equipment and tools" also provided for accelerated development and production of ChPU devices for all main groups of industrial machining equipment (machine tools of various types, forging-press and foundry equipment, automatic lines and machining centers and sections) for subsequent years. The existing scinatific basis in machine control theory and in production operation programming theory and the extensive experience of development and complex debugging of complex electromechanical machine tool systems-UChPU-permit complex solution of these problems at a high scientific and technical level.

The development and further improvement of the State System of Industrial Devices and Means of Automation (GSP), which encompasses all the most important functional groups of measurement, monitoring and regulation hardware for production processes and which comprise the basis for construction of ASU TP [Automated production process control system] of various classes and designations, was continued during the 10th Five-Year Plan. Based on GSP standards and using new physics and technological principles, a large number of types of sensors of physical values (pressure, flow rate, level, temperature, electric output and so on), normalizing and functional measuring converters, servo mechanisms, local and group regulators, means of telemechanics and other devices, including those oriented toward use under severe operating conditions, was developed and put into production.

Expansion of industrial output of efficiently built series of GSP instruments and devices technically compatible to each other made it possible to design and use the most diverse and complex monitoring, regulation and control systems for the needs of practically all sectors of industry with analog and analog-digital nature of production and primarily of power engineering, ferrous and nonferrous metallurgy, chemistry, oil and gas production and petroleum refining.

The nomenclature of GSP devices, considerably renewed during the 10th Five-Year flan, numbers more than 2,000 types of instruments and devices and their production volume reached approximately two billion rubles in 1980. The main specifications-precision of monitoring and regulation, ranges of measured values and reliability-improved significantly. GSP devices and specialized unitized complexes of instruments built with observation of GSP standards now make it possible to measure and regulate more than 600 varieties of physical values and production parameters (including those by indirect methods) over a wide range of values and under different operating conditions.

The domestic GSP, coordinated by basic principles and standards with the national systems of CEMA members, has no equal in the worldwide practice of instrument building in functional completeness, scope of measurement, monitoring and regulation problems, universality of applications, level of unitization, unification and standardization, metrological support and scales of production and use in the national economy.

5

An extensive program of investigations to establish and organize output of measuring devices and means of automation for different industries in agriculture and processing of agricultural products has been organized and is being implemented successfully. The output of complete agrochemical laboratories, automated weighing and weighing-proportioning equipment, analytical equipment, means of automation for animal husbandry complexes and for irrigation systems and other measuring and regulating devices has been expanded.

The nomenclature of devices supplied to agriculture in 1980 numbered more than 350 and investigations are continuing in this field.

One of the most important statewide programs consists of a complex of investigations to establish and develop devices for scientific research and means of automation of scientific experiments.

Realization of the most important national economic task posed by our party on transforming science into a direct productive force, increasing the rates of development and intensifying the effect of achievements of the fundamental sciences on the rates of technical progress in the national economy required accelerated development from instrument builders in developments and assimilation of production of many of the most complex devices and equipment for outfitting scientific institutions.

An extensive program of investigations to establish and organize production of many types of devices for scientific research (including those based on new physical principles), new means of automation of scientific experiment using mini- and microcomputers and programmable digital equipment for measurement and analysis of the composition and structure of substances and materials, was prepared and is being successfully implemented jointly with the USSR Academy of Sciences. A considerable number of scientific organizations and enterprises of the sector participates in development and production of devices for scientific research. More than 100 types of complex devices for scientific research, including mass and radio spectrometers, x-ray analyzers, chromatographs, electrometers, electron microscopes, structural analyzers and other scientific apparatus, were developed and put into production during the 10th Five-Year Plan jointly with institutes of the USSR Academy of Sciences.

Means of automation of scientific experiment--measuring and calculating complexes with programmable measuring apparatus in CAMAC standards and developed software and metrological support--have been established and are being produced. More than 42 percent of the devices for scientific research are produced with the state Emblem of Quality. According to the draft of the "Main trends of economic and social development of the USSR for 1981-1985 and for the period up to 1990" and according to the growing needs of Soviet science, this complex of scientific research and experimental design work, which enriches our design organizations with new progressive ideas and which actively affect an increase of the technical level of all instrument building, will be developed at high rates during the forthcoming five-year plan.

A great deal of attention was devoted in the sector during the 10th Five-Year Plan to further development of production and increase of the technical level of the clock industry—the traditional basic sector of precision mechanics. Production of

#### FOR OFFICIAL USE ONLY

service clocks was increased 1.2-fold during the five-year plan and reached 58 million units in 1980. Models of mechanical clocks produced were completely renovated and production of highly accurate electronic crystal watches was organized. Much has been done to improve the technology of clock production: automated assembly of clocks using manipulator robots (USSR State Prize for 1979), laser machining of jewels, automatic timing of clocks using computers and much more were organized. Mowever, even greater changes in this traditional field are expected during the lith Five-Year Plan with regard to a further significant growth of the specific weight of electronic clocks and the entry of the modern advances of electronics into the clock industry.

An important factor in development of the sector and its active effect on the rates of technical progress in the national economy was further expansion of work in the field of development and introduction of automated control systems (ASU). ASU were developed for all levels of control: production units, plants, enterprises, combines and production associations, sectors, nonindustrial facilities and territorial complexes. The range of problems solved was expanded significantly and the technical level of ASU for production processes and sector ASU was increased. Systems based on modern scientific principles of construction and functioning were established: direct digital control, adaptive and integrated, multilevel hierarchical and also complex queueing systems and the first "distributed control" systems. Such large ASU as the ASU of the PO [Production Association] Uralmash, PO Rostsel mash and the complex of automated systems of ASU-Olypiada became operational.

Automation of control of production processes, units and plants based on the use of modern computers is the main trend of scientific and technical progress in sectors of industry with analog and analog-digital nature of production. The accumulated experience clearly shows that development of ASU TP for many large-capacity production facilities now operating ensures a significant increase of their operating efficiency by operational optimization of control processes, which is essentially impossible when using traditional methods of monitoring and local automation.

The scientific research and planning organizations of Minpribor concentrated their efforts during the 10th Five-Year Plan primarily on development of pilot ASU for highly productive large-capacity units of new types in power engineering, ferrous and nonferrous metallurgy and the chemical, petroleum refining and petrochemical, the petroleum, gas, coal, pulp and paper and construction materials industries. Fore than 150 highly efficient pilot ASU TP for new production facilities in the inficated sectors were established and put into operation through the efforts of our scientific collectives jointly with the customers.

Among them are ASU TP of nuclear energy blocks with capacity of 440, 600 and 1,000 YV at the Beloyarskaya and Novovoronezhskaya Nuclear Power Plants, the ASU of the world's largest thermal energy unit, rated at 1,200 MW, at the Kostromskaya GRES, the largest blast furnace No 2 of the Krivorozhstal' Plant imeni V. I. Lenin, the universal beam rolling mill of the Nizhniy Tagil' Metallurgical Combine imeni V. I. Senia. The concentration plants of the Zyryanovsk Lead Combine, gas lift production of petroleum at the Association Kaspmorneft' and many others.

Dowestic and forcion experience shows that the greatest deficiency in utilization of all modern methods of control, monitoring and regulation of the corresponding hardware-from control computers to servo mechanisms—is achieved in the national economy with complex, systematic organization of interaction of this hardware with the

7

monitoring and control object, including the technological personnel of this facility. Therefore, the activity of our scientists, designers, planners, installers and developers of devices and means of automation who participate in establishment, introduction and subsequent development of ASU of various classes and designations, is the most important essential aspect of the activity of the sector. Significant results were achieved during the 10th Five-Year Plan in improving the methods of this work.

Based on generalization of the developments of a large number of basic objects, standard design solutions and applied program packs used extensively by organizations and enterprises of other sectors in development of systems, were developed. Methods of ASU design and and software for them, scientific methods of building integrated and multilevel ASU that encompass organizational-production and technological processes at enterprises were worked out and developed. All-Union stock of general-purpose applied program packs and libraries of standard algorithmic and program modules for ASU TP of a number of sectors of industry were established and developed, automated software generation systems for ASU TP were put into operation and scientific experimental centers for testing pilot systems are functioning. Further development of the indicated trends and a significant increase of the finite national economic effectiveness in complex utilization of all means and methods of modern automation are one of the most important tasks of the instrument builders during the 11th Five-Year Plan.

Fulfilling the decisions of the 25th CPSU Congress, the instrument builders devoted special attention to development and implementation of measures which enhance the technical and economic efficiency of production. Specifically, they include further improvement of management of the sector as a whole and of its individual enterprises, an increase of the level of the operational rhythm of plants, introduction of highly productive automatic equipment and new production processes, introduction of the complex product quality control system at practically all plants, improvement in the use of basic funds and capital investments, extensive use of microelectronics in development of new devices and means of automation, including organization of certain types of integrated circuit production, development and introduction of ASU TP at plants of the sector, development of the instrument base of the sector, local production of nonstandardized production equipment and specialized cooperative production of assemblies and parts for general sector application (casting, fastenings, sockets, construction materials, printed circuit cards and so on). Modern methods of automated design and monitoring (using computers) of printed circuit cards and installation panels have been developed and are being used successfully at many plants, design of production equipment is being automated at some plants and machine output of production documentation is being organized.

Implementation of measures to increase production efficiency made it possible to complete fulfillment of the plan of the 10th Five-Year Plan on the growth of product volume ahead of schedule. Devices, means of automation and computer equipment worth more than 310 million rubles were produced above the five-year plan. The task of the five-year plan on increasing labor productivity was overfulfilled. Consumer goods worth 117 million rubles above the task for the five-year plan were manufactured. A total of 53,000 tons of ferrous rolled metals, 40,000 tons of nonferrous rolled metals, 57.3 million kW·hr of electric power and 100,000 Gcal of thermal energy were conserved during the 10th Five-Year Plan. The scientific research institutes, design offices and plants of the sector fulfilled 283 tasks of the state

plan for development of the national economy of the USSR on assimilating the production of the most important devices and means of automation of new types during the five-year plan, including 55 ahead of schedule, and more than 100 tasks on 89 problems according to programs of GKNT [State Committee for Science and Technology] on solution of the most important scientific and technical problems.

Considerable work was carried out on automation and mechanization of production at plants of the sector: 80 shops were mechanized in a complex mather, more than 650 mechanized continuous production conveyor lines were put into operation, 250 automatic and semiautomatic lines and more than 450 machine tools with ChPU were put into operation.

The decree of the CPSU Central Committee "On the socialist competition for a worthy welcome of the 26th CPSU Congress" aroused new creative enthusiasm among the collectives of instrument builders, who organized a socialist competition to fulfill the tasks of the 10th Five-Year Plan ahead of schedule and new labor achievements. The brigades, sections, shops, enterprises and organizations adopted increased socialist pledges and strived to work in a shock-labor and communist manner.

Among the collectives in the vanguard of instrument builders are the Second Moscow Clock Plant, the Kiev Production Association Tochelektropribor and Production Association Elektronmash imeni V. I. Lenin, the Moscow Production Association Manometr, the Orel Production Association Prompribor and the Production Association Leningrad Electromechanical Plant. These and many other collectives reported fulfillment of the tasks of the 10th Five-Year Plan ahead of schedule.

Thus, the collective of the Kiev Production Association Tochelektropribor completed the tasks of the 10th Five-Year Plan in labor productivity in July 1979 and the tasks in production volume on 3 October 1980. They produced and sold products worth more than 15 million rubles above the tasks of the five-year plan. The entire increase in the volume of production was achieved as a result of increasing labor productivity.

Many thousand workers of the sector completed their personal five-year plans ahead of schedule. More than 35,000 leading workers, approximately 400 brigades, 100 rections and shops reported fulfillment of their own pledges to complete the tasks of the 10th Five-Year Plan as early as the 110th anniversary of V. I. Lenin's birth. More than 80,000 production leaders successfully completed the 10th Five-Year Plan by the 63rd anniversary of the Great October Socialist Revolution.

Products worth 85 million rubles above the plan were sold throughout the sector as a whole in 1980, which is 25 million rubles more than was envisioned by the additional pledges adopted in honor of the 26th CPSU Congress.

The scientific research, design-production and planning organizations of the sector have also made a significant contribution to the increase of production efficiency during the socialist competition in honor of the 26th CPSU Congress. The scientists, engineers and workers of the Institute of Control Problems (Moscow), the Severodonetsk NFO [Scientific Production Association] imeni 25th CPSU Congress, NIIteplo-pribor [Scientific Research Institute of Heat Power Engineering Equipment], VNII [All-Union Scientific Research Institute] of Electric Measuring Devices (Leningrad), the Vilnius Production Association Sigma, MNIPI [Moscow Scientific Research and

9

Planning Institute of Network Program Planning and Control Systems for Industry and other leading organizations of the sector came to the congress with important achievements in development and assimilation of new equipment at the level of the best worldwide models.

Being guided by the draft of the "Main trends of economic and social development of the USSR for 1981-1985 and for the period up to 1990," published by the CPSU Central Committee, the instrument builders aim for new boundaries in development of the sector with high labor enthusiasm.

Intensive development and a further increase of production of instruments, means of automation, high-speed control and computer complexes, primary development of progressive and more modern types of instrument production and achievement of higher qualitative level and efficiency of ASU under development are planned. Extensive automation and complex mechanization of instrument building processes will be implemented and the fraction of manual labor will be reduced significantly, including that on specific, "thin" assembly and monitoring-checking operations. Microelectronic technology and modern microprocessor equipment will become the determining base for development of instrument building in all its main trends.

The new level of technical equipping not only of sectors of heavy industry and machine building but also of agriculture, the construction industry, transport, medicine, public services and environmental monitoring during the 11th Five-Year Plan require development and production of many types of essentially new devices and means of automation oriented toward the specifics of each user. This is primarily related to sensors of physical values and different production parameters, which largely determine the capabilities of developing highly efficient modern control systems. Special attention will be devoted to development and production and to significant expansion of the efficient nomenclature of various types of sensors.

The most important integral characteristic of the technical level and quality of instrument building products is the operational reliability of the devices and means of automation. The significant results achieved in this direction permit us to plan new tasks for the 11th Five-Year Plan for all groups of articles with regard to finite national economic estimates of this activity, which encompasses all stages of development, production and maintenance of means of automation.

welcoming the 26th CPSU Congress with high labor enthusiasm, the instrument builders assure the CPSU Central Committee that they will make a worthy contribution to implementation of the program planned by the Party for further development of the national economy of our socialist motherland.

COPYRIGHT: "Izdatel'stvo "Mashinostroyeniye". "Pribory i sistemy upravleniya", 1981 [122-6521]

6521 CSO: 1863

FOR OFFICIAL USE ONLY

UDC 65

SOME PROBLEMS OF SCIENCE IN DEVELOPMENT OF CONTROL SYSTEMS

Moscow PRIBORY I SISTEMY UPRAVLENIYA in Russian No 2, Feb 81 pp 6-8

[Article by Academician V. A. Trapeznikov, director of Institute of Control Problems]

[Text] The science of management, which occurred approximately 100 years ago, began to develop especially rapidly during the 1950s and now encompasses a wide range of problems related to management of engineering, socioeconomic and biological objects.\* The science of management encompassed a number of new fields during the past few years. These are problems of classical sections of the theory and those sections which one may also now regard as classical: optimum, adaptive and logic management, the problem of stochastic systems, identification, machine modelling, construction of man-machine complexes, design automation and automation of scientific research. Management theory has penetrated many fields of the industrial and nonindustrial sphere of the national economy and has encompassed management hardware, especially that developed on the basis of computers. Such achievements as missile and space-craft control, automatic docking and solution of many other related problems became possible only on the basis of automatic control theory.

Let us dwell on some of the future problems of development of science and technology.

As is known, science is developing in an evolutionary manner, step by step, but jumps occur from time to time which introduce a new quality into the process of development. I would like to dwell on these intermittent points of its growth. On the other hand, without falling into predictions of fantasy, one can talk about "intermittent" trends that already have adequate scientific and technical bases that are real for use in the national economy during the 11th Five-Year Plan.

It is known that there were several steps of scientific and technical transformations related in one way or another to management problems in the development of mankind. The first industrial revolution was characterized by replacement of physical human labor by the work of machines. It subsequently turned out that many macines, especially steam machines, are unable to operate without constant control and this caused the appearance of automatic regulating devices which freed man to a significant degree from performing a number of functions of mental activity. Automatic control systems gradually encompassed various fields. Control hardware was also improved simultaneously, freeing the mind of man. Finally, computers appeared which provide an enormous jump, specifically, in the sphere of control.

11

Based on the author's report at the Eighth All-Union Conference on Control Problems at Tallinn, held on 6 October 1980.

#### FOR OFFICIAL USE ONLY

We feel that a period has now come when computers and other devices should relieve man of part of his mental activity in development of control systems themselves, which is undoubtedly a qualitative jump. The appearance of new hardware and the fundamental change of the existing structures or configurations of control systems usually result in the appearance of new theoretical approaches and this in total provides a jump in development of our science. These problems will be primarily touched on in this article.

Let us formulate some requirements on control systems which reflect the interests of the national economy and on the other hand, which take into account real situations encountered in life. These are primarily the characteristics of the producer and user.

From the national economic viewpoint, there are no principal antagonistic contradictions in our social system between the user and the producer, since they are links of a common closed sphere of circulation of property, energy and information and they work for the common good of the state. However, two psychologically different approaches to the concepts "consciousness," "discipline" and so on can be noted in real life, and namely: the approach of the producer and the approach of the user. The producer may be a plant producing a means of control and KB [Design office] and NII [Scientific research institute] which produce designs, algorithms and programs.

Unfortunately, the following principle is predominant in the producer's psychology in many cases: fulfill the plan according to the confirmed technical tasks, turn over the product, perhaps even with reduced quality, and sign the report on fulfillment of the plan. What will happen to the product in the future and who will correct the deficiencies is of little concern to the producer in many cases. Let us assume that almost everyone has encountered a similar situation, specifically upon introduction of our ASU [Automated control system], without mentioning construction facilities.

With regard to the specifications for a product, they are usually closer to the concept "what can be done" than to the concept "what needs to be done."

The user's position is diametrically opposite. He wants to have a product that is at a modern level so that operation of the product proceed with the least fuss. Exactly one of the reasons that make it difficult to utilize control systems is failure to consider the user's requirements. An attempt to force the user to use systems inconvenient for him by administrative pressure or planning measures is unsuccessful and only creates a vision of activity.

In the final analysis the producer's and user's positions reduce to problems of quantity on the one hand and quality on the other and to contradictions related to both concepts. The fact is that a high-quality article will always be more labor-consuming than a low-quality article at some level of design, technology and organization of production.

I am in the position of the user and I will formulate the general requirements which the user places on control systems from this viewpoint.

The life of a product related to control usually consists of three phases: 1) development, which may include design and adjustment, 2) operation and 3) modernization related either to a change of the controlled medium or to the appearance of new, more improved solutions which sometimes appear even during design. The user's requirements to which I turn are related to all three phases of a product's life.

We feel that a product in general use, without mentioning its quality, should meet at least four criteria.

The first criterion is simplicity and convenience of use. This means that there should be the capability of assimilation without recruitment of scarce, highly qualified specialists. The periods of training and assimilation should be minimal, preferably on the order of several weeks. Of course, this does not contradict the need to increase the general scientific level of specialists.

The second criterion is the capability of modernization. It is known that the structure of a controlled object, its properties and finally the volumes and formats of the accompanying documentation are subject to various changes during operation and sometimes even during design. If a control system does not provide for these capabilities, it passes from a progressive to a conservative factor.

The third criterion is viability. This concept is somewhat broader than that of "reliability," since it includes a number of concepts of "reliability," including the concept of the probability of failure-free operation. The requirements on the average length of failure-free operation depend on the controlled object, which should be calculated in thousands of hours under ordinary conditions, with the capability of rapid diagnosis of the point of damage and rapid replacement of the damaged assembly. The total lifetime of a control system in industry should be determined at least as 10-15 years. The concept "viability" envisions the efficiency of a system, perhaps with some deterioration of control quality with external emergency effects on the system, while the theory of viability specifically considers the dynamics of the development of emergencies.

The complexity of control systems increases as the complexity of controlled objects increases. For example, the control systems of nuclear power plants may contain thousands and sometimes tens of thousands of sensors and other similar components. It is clear that a large number of components leads to a reduction of the viability of a system. Science noted the ways of increasing viability by redundancy, voting, diagnosis, correct design of the structure with regard to more or less important sections and finally by finding the most reliable methods of measurement.

Mowever, science alone cannot provide the proper reliability of complex systems. The sources of reliability lie in correct design, use of high-quality materials, good technology and organization of operation by operation checking during manufacture. This makes a control system more expensive and increases the laboriousness of its manufacture, but this increase in cost will be repaid with interest by reducing the idle times of the basic expensive controlled equipment, for example, an electric power plant. One can say that "quality is more economical than quantity" from the state's viewpoint.

We note that the proper significance is frequently not given to problems of reliability and viability. Thus, for example, one can point out cases when diagnostic

13

and some other circuits were thrown out for purposes of simplification in development of computers. It is clear that this led to a sharp reduction of the operational characteristics of the machine.

The fourth criterion is economy provided by low capital investments, low operating expenses and gradual introduction of the control system into operation, beginning with the most efficient tasks. When calculating economy, one should not forget the different times of initial expenditures and the economy achieved.

It is known that the relative cost of hardware in a control system is reduced each year, while the fraction of the cost of design and programming increases, reaching 60-70 percent of the total expenditures for the system. Some foreign companies even offer computers to users free of charge, requiring payment only for the software. Development of automated design, programming and debugging systems is becoming exceptionally timely. It is for this reason, talking about the possible points of growth, that one should dwell on these problems, i.e., on problems which assist the intellectual creative activity of man.

The process of design is diverse and strictly speaking begins with research and predesign work in laboratories or under other conditions. A qualified design requires preliminary analysis of the facility to be automated, gathering of its characteristics and compilation of a model. This is a laborious and prolonged process and identification devices connected to a production or different object without interruption of its functioning, which may relate to automation of the experiment, come to one's aid here.

Turning to automation of design as to one of the important points of growth, its diversity should be noted. Automation of design begins with design of components such as microcircuits and BIS [Large-scale integrated microcircuit], design of machine assemblies and finally ends with design of entire systems, for example, of control systems.

The concept of SAPR [Automated design system] is rather diffuse and usually includes design of material systems: microcircuits, tools, machine tools, architectural structures and so on. During the past few years SAPR, utilizing machine graphics in most cases, have been developed throughout the world. They have been developed by tens of NII and KB in our country. Unfortunately, the exchange of information in the field of SAPR is difficult since some leading specialists regard it as a professional secret. As a result, there is no unanimity and standardization of requirements on SAPR, they are developed with respect to various types of computers and different classes of problems, have different degree of complexity and sometimes require prolonged assimilation.

As a prospect, one should turn attention to development of machine graphics systems which provide effective interaction and dialogue of the user with the computer, with a language which approximates a natural language, systems simple to operate and designed for rapid assimilation by an untrained user. The use of different computers should be provided, beginning with minicomputers, without interfering in their operating system, and the use of various peripheral devices should be provided. The descriptions of user's problems compiled for computers of the same type should be suitable without any changes at all for other computers. The system should be open, should permit free build-up, flexible unified integration with the user's

14

problem-oriented software, and should provide connection of different applied programs and their modules. Of course, the system should have access to actuating devices such as machine tools with program control and so on.

We note that there are bases for this type of system that are rather simple, developed within 1-2 weeks and which meet the above criteria. These investigations are in the sphere of observation of one of the technical committees of the USSR National Committee on Automatic Control.

It would be interesting to consider the problem of what a common base, the "core" of automated design is to which the program modules, optimization programs and so on should be connected. This would facilitate development of a common, and to a significant degree unified SAPR.

We have already noted that the increasing laboriousness and scales of design become an obstacle for further expansion of ASU utilization, making it necessary to automate their design and programming. These investigations are being conducted both in the USSR and abroad. Part of the organizations is proceeding along the path of standardization—development of standard applied program packs, each of which corresponds to solution of one or another problem. This group also includes development of standard program modules.

Standardization of programs and program modules is undoubtedly a useful, but slowly proceeding process. The efficiency of standardization depends on the identical nature and stability of objects, but expenditures for tying in standard design solutions are frequently comparable to expenditures on the original design.

Talking about the stability of controlled objects, we note that the flaw of many concepts of design and utilization of ASU is concealed here. It turns out that most ASU are considerably more dynamic than is usually assumed. Control objects are modified during prolonged design and debugging and are improved during operation and their form is changed, including their structure and the format of the accounting documentation. Many examples can be cited when requirements on a system change as a result of many years of design and it was obsolete at the moment it was ir duced. The inflexibility of hardware and software places an obstacle in from the making the necessary changes and postulation of new problems, and even more so if the user has no qualified programmers.

Should one be amazed by the fact that if the user has no flexibility of programs, he loses interest in the ASU or that "psychological resistance" even occurs? Not so much the users and the "user" qualities of ASU are guilty in this case. Based on this, one should develop a new approach to automation of design in order to fulfill the following requirements:

the speed of design of an ASU with the simplest method of preparation of the input information and reduction to a minimum of the length of the analysis-development-design-implementation cycle;

orientation to the user, provision of the capability of loading the system with problems in the order of their decreasing efficiency, of modernizing the system and inclusion of new problems in it through one's own efforts, without inviting "intermediaries" and highly qualified programmers;

15

1

#### FOR OFFICIAL USE ONLY

direct automatic printout of the control programs by the system itself.

Solution of these problems is quite realistic and can be confirmed by the examples of systems which meet these requirements.

Throughout the world, qualified specialists study production processes from the viewpoints of control, investigate the properties of mathematical models of processes and develop ever more effective control algorithms. This is tedious and expensive work. To facilitate the utilization of these scientific results, scientists strive to classify control objects and to standardize on this basis models of them and methods of control.

It would seem that when designing a specific ASU TP [Automated production control system], it would be sufficient to take the corresponding scientific material from the enormous arsenal and to begin design. Unfortunately, this frequently cannot be done. The reason is that objects which are typical at first glance, are not identical in practice, require additional investigation and alter their characteristics during operation.

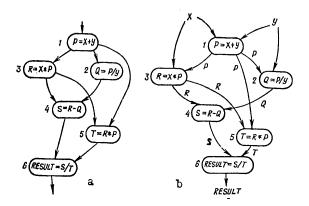

In order to cope with this and with similar factors, one of the universal principles —adaptation—is employed. As is known, adaptation theory has achieved extensive development. One of the implementations of this principle was a control system with identifier in a feedback circuit. This system, executed in the form of a computer with set of sensors and outputs to actuating mechanisms, is connected to the controlled object. It "observes" it, constructs a model of the object within itself, selects its parameters and is thus gradually taught. When the model with all parameters of the object is built—in, the system changes to the control stage, at the same time refining the parameters of its own model. Many years of operating experience at a pipe—rolling plant proved its effectiveness and reliability. The system has a number of valuable properties. It frees the creative and physical efforts of man and reduces the length of design and debugging.

The concept of the system has now been realized in different countries (the mentioned system in the USSR was apparently the first in time). This concept is now being utilized in the United States, Sweden, West Germany and other countries. We feel that this concept is one of the very promising trends, and even more so since it is applicable to control of facilities of the most diverse physical nature.

An interesting trend are teaching programs, by means of which problems of large dimensions can be solved on the basis of nonclassical methods, automatically utilizing the parameters of similar problems of lesser dimensions.

Let us now dwell on the jumps related to the appearance of new hardware. An important "intermittent" trend in the entire world is microprocessor systems and local networks of microcomputers. This trend is unusually broad and it relies to a significant degree on technology, while the control problems rely on development of the theoretical fundamentals of constructing these systems.

The use of microprocessors may in the near future lead to fundamental changes in control systems. During the past 30 years, control theory has proposed a set of complex and precise optimum control algorithms, while in practice simple, but

16

nonoptimum laws of regulation were mainly used due to the difficulty and uneconomical nature of realizing them.

The use of microprocessors, microcomputers and programmable controllers as direct digital regulators, the behavior of which is determined by the program stored in the memory of the microcomputer, permits an expensive realization of algorithms of any complexity in distributed production control systems, which stimulates further theoretical investigations.

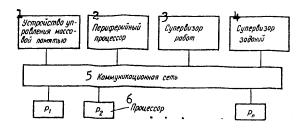

Decentralized data processing systems with distributed configuration based on local microprocessor networks or local microcomputer networks have a number of advantages such as high viability, flexibility and the capability of reconfiguration. They permit qualitatively new solution not only of many problems of technical control, but also a number of problems in organizational systems.

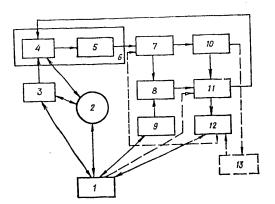

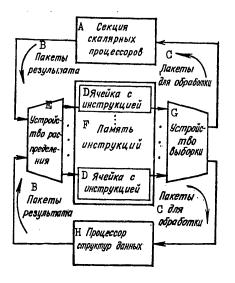

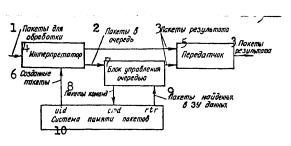

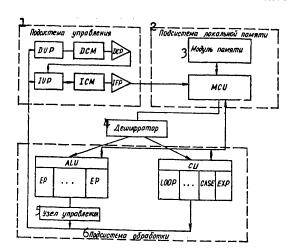

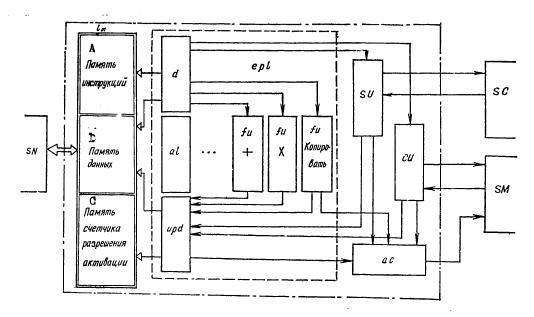

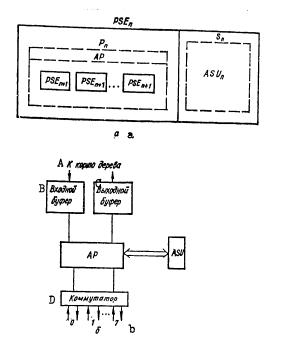

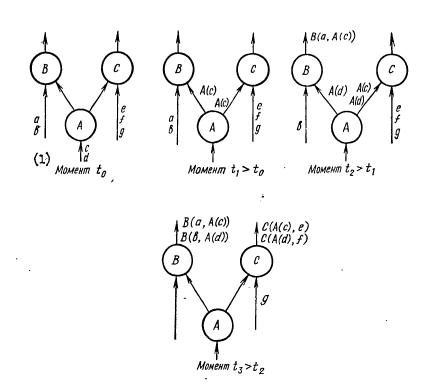

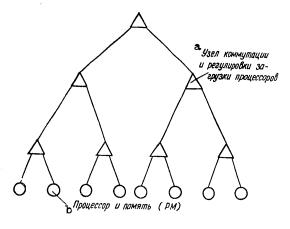

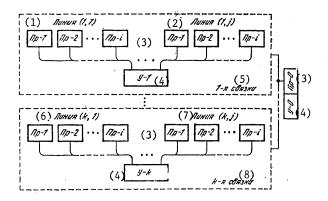

Let us dwell somewhat on a trend related to the appearance of new hardware, namely, on problem-oriented control computer complexes with nontraditional structure. This is a family of computers of type PS with homogeneous multiprocessor structure automatically rearranged during problem-solving. The family of PS consists of several models of different calculating power and different specialization.

Let us assume that most readers are familiar with this problem, already realized on small models of PS serially produced for control of production processes. Higherend models will be serially produced during the current and subsequent years. A geophysical computer complex described in this issue of the journal has been constructed on the basis of one of the higher-end models of PS. I feel that an important future belongs to machines with rearrangement structure in development of multiprocessor highly productive failure-free fourth-generation control computer systems and that they are undoubtedly related to the jump-ahead phenomena in our science and technology.

Which of the enumerated intermittent phenomena are actually "growth points" and which of them will lead to qualitatively new changes in the science of control and which will point the way to the future.

After all, forecasting is a difficult task and of course the indicated list does not encompass all the trends of our science and it primarily does not indicate the development of a wide range of fundamental research in the field of control theory. However, it is impossible to fully encompass these problems in one article.

In conclusion, a few words about a much broader control problem, unfortunately unformalized and consequently unsolved even by using the most powerful computer. This is the problem of management in the national economy and namely: how to place enterprises and other organizations into conditions in our rigidly planned economy when most of them will aspire to maximum rates of technical progress?

This problem, which we have faced for many years, and specifically mentioned in the author's article in PRAVDA, dated 20 March 1980, goes far beyond all that has been mentioned in its significance.

It is pointed out in the indicated article that technical progress, necessary on the whole to the national economy, is of insufficient interest to individual links of

17

the science-national economy chain. Of course, implementation of the decree of the CPSU Central Committee and the USSR Council of Ministers "On improvement of planning and intensification of the effect of the economic mechanism on increasing production efficiency and work quality" will improve this situation in time.

The difficulty of solving the problem includes the fact that we do not adequately take into account the role of man in the control system. Moreover, every person has his criteria of behavior and his own "scale of values." The main thing for some is acquisition of something in the material or prestige plan and the danger of losing this; in others it is a quiet life with minimization of labor; and in still others it is an aspiration toward creativity and enthusiasm. These people simply cannot live otherwise and they must create something new. Technical progress is based on these very enthusiasts of the most diverse hierarchical level and is to them that we are obligated for the greatest scientific and technical achievements, since there are no stimuli in our economic mechanism which automatically accelerate technical progress.

It was mentioned above that increased quality at the given level of technology also requires increased labor expenditures, exactly the same as an increase of product quality. Consequently, both one and the other is related to an increase of labor expenditures. And what does one do with the capacity of an enterprise fixed and with utilization of available reserves?

Thus, quality is in contradiction to quantity. What is the solution? Only in technical progress and in new scientific and technical ideas which advance a product and the enterprise to a higher level!

We feel that with the existing system of management, the basis of the indicated difficulties is a common factor: this is the actual many years of underestimation of technical progress, improper consideration of its position in the common "scale of values" and failure to consider the main laws of control. Quantity is frequently regarded as of paramount importance at different levels in planning, while problems of quality and of new technology are placed in second and third positions. This generates "lazy thinking" and leads to the temptation to copy foreign technology, which in turn predetermines our lag.

A few more words about man. With all the difference of natures, most people cannot be indifferent how society and managers evaluate their work; therefore, they act, taking into account to one or another degree the "scale of values" of managers, considering what they will be praised or criticized for and for what their bonuses will be increased or reduced.

Based on this, under our modern conditions, without touching on serious transformations, the most effective would be the following: quality and scientific and technical progress rather than quantity should be decisively moved to the forefront in planning, operational control and stimulation. In the final analysis, it is this that determines the improvement of a product and labor productivity. The measures which create an acute self-interest and acceleration of scientific and technical progress also primarily determine the prospects for accelerated development of our national economy.

Of course, evaluation of scientific and technical progress is a difficult matter and psychological as well as scientific and technical difficulties are encountered

18

# FOR OFFICIAL USE ONLY

here. Nevertheless, approaches and solutions can be found with serious postulation.

Problems of management in the national economy with regard to common laws of control theory and problems of man in the control system, of evaluation criteria and of the structures of the system, as before, remain the most important problems awaiting their solution during the 11th Five-Year Plan.

COPYRIGHT: Izdatel'stvo "Mashinostroyeniye". "Pribory i sistemy upravleniya", 1981 [122-6521]

6521

CSO: 1863

19

#### FOR OFFICIAL USE ONLY

UDC 65:681.3"71"

TOWARD NEW POSITIONS OF AUTOMATION OF CONTROL IN BASIC SECTORS OF INDUSTRY

Moscow PRIBORY I SISTEMY UPRAVLENIYA in Russian No 2, Feb 81 pp 9-11

[Article by Candidate of Technical Sciences M. P. Babin, chief of All-Union Production Association Soyuzpromavtomatika, and Candidate of Technical Sciences A. A. Levin, chief engineer of VPO Soyuzpromavtomatika]

[Excerpts] The expenditures for individual components for development of ASU TP [Automated production control system] are now evaluated in the sectors of industry under consideration by approximately the following relations:

applied software (mathematical modelling, control algorithmization, design and machine programming) comprises 30 percent;

acquisition of measuring and control apparatus comprises 30 percent;

acquisition of control computer complexes--UVK (including devices for communicating with the object and operating personnel) comprises 20 percent;

performance of installation and adjusting work comprises 20 percent.

COPYRIGHT: Izdatel'stvo "Mashinostroyeniye". "Pribory i sistemy upravleniya", 1981 [122-6521]

6521 CSO: 1863

#### FOR OFFICIAL USE ONLY

UDC 681.3.004

PROBLEMS ORIENTATION OF COMPUTER COMPLEXES OF THE INTERNATIONAL SMALL COMPUTER SYSTEM

Moscow PRIBORY I SISTEMY UPRAVLENIYA in Russian No 2, Feb 81 pp 20-23

[Article by Doctor of Technical Sciences G. I. Kavalerov, USSR deputy minister of instrument making, means of automation and control systems]

[Text] The most important features of small computers (mini- and microcomputers) which determine their widespread and mass use are accessibility to the user (in cost, overall dimensions and programming and operating simplicity) and the capability of adjusting information processing and automation of control of various types of facilities to specific problems.

Computers of this class, as is known, provide effectiveness of automation of both complex and large as well as relatively inexpensive machines, units and scientific equipment and make development and use of individual ("personal") computer complexes economically justified for scientific workers, engineers, economists and specialists in the field of control.

Design of diverse decentralized, distributed and network structures, feasible distribution and the use of the calculating capability of large universal computers and design of hierarchical control systems are provided when using small computers. This in turn determines the very extensive diversity of requirements which are placed by specific spheres of application on computer equipment of the given class.

Detailed analysis of the broad spectrum of diverse applications of minicomputers was made with regard to these features of small computers even during the first stage of development of the SM EVM [International small computer system] and the priority areas of application were selected in which the hardware and software of the SM EVM make it possible to achieve the greatest technical and economic effect.

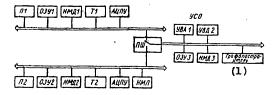

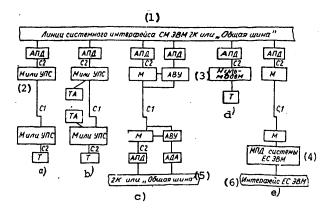

These areas include control of production processes and production equipment in industry (ASU TP), automation of design in industry and construction (SAPR) and automation of scientific experiment (SANE).

All the principal engineering and organizational decisions on configuration of the computer, block-modular design, selection and standardization of interfaces and structures, nomenclature of hardware and composition of software and specialization, cooperation and development of SM EVM production were adopted with this orientation to these areas of application.

21

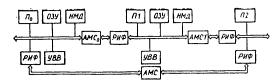

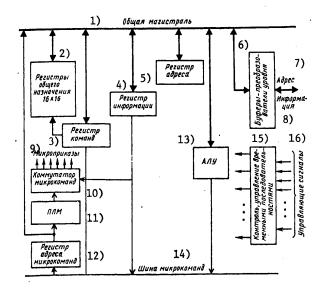

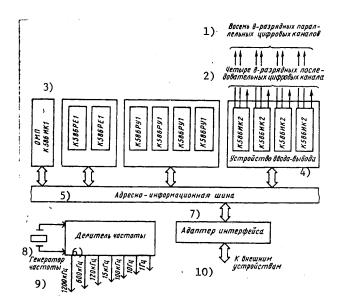

The SM EVM models of the first unit produced in large series have sufficiently high productivity (up to 800,000 operations per second), expanded OZU [Internal storage] capacities (up to 128K words) and a wide nomenclature of peripheral devices including modular devices for communicating with the facility [1-3].

The adaptability of the computer complexes of the SM EVM to user problems in different areas of application is provided by:

the unit (modular) principle of designing all the hardware with provision of systems compatibility;

efficient design of a number of peripheral devices and functional blocks with characteristics which provide continuity for the user during improvement of them and during development of the system;

developed general and specialized systems software for different configurations of computer complexes and their operating modes (10 varieties of operating systems, software for organization of remote processing, for multimachine complexes, debugging equipment, test programs, drivers for control of nonstandard peripherals and so on);

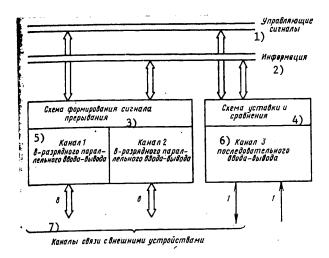

development of specialized intrasystems communications equipment and specialized peripheral devices (for example, USO [Unified organization systems] and CAMAC controllers, graph plotters, information readers, concentrators, terminal stations and so on);

continuity of software both with the preceding modular system of computer technology (ASVT-M) and with development of the SM EVM.

Rather extensive experience in development and use of control and information computer systems for different objects has now been accumulated.

The total number of computer complexes based on ASVT-M models (the M-6000, M-7000 and M-400) and the SM EVM exceeds 10,000 units. The volume of accumulated user software is estimated at not less than 700 million instructions. More than 12,000 operating personnel and programmers have been trained.

Achievement of the greatest efficiency for the mass user of small computers by means of problem orientation of them under conditions of the growing scales of production and application of SM EVM in the national economy is the most timely problem and main feature of technical policy in development and production of SM EVM.

The materials of questionnaire examination of ministries and agencies were analyzed to evaluate the prospects for 1981-1990 for using computer equipment of this class, to determine the most effective spheres of application and to systematize the user requirements. Economically feasible use of mini- and microcomputers for automation of control and information processing at different facilities of the national economy was evaluated from the results of the analysis, the readiness of facilities for effective automation was determined and the number of these facilities and the required number of computer equipment was estimated.

According to data of sectors of industry, approximately 20,000 highly productive production processes, powerful units and plants will be operating by the year 1990, for which design of ASU TP using computers is economically feasible. The potential need for automation using computer equipment is estimated at several tens of thousands of facilities in the nonindustrial sphere (transport, communications, construction, agriculture, health and so on). The need is estimated at approximately the same number of facilities in the sphere of automation of engineering design, automation of scientific experiment, testing of industrial products and programmed occupational training and retraining of workers.

Moreover, automation of various machines, devices and apparatus with local (decentralized) information processing requires a large number of built-in microcomputers and microprocessors. There are now some preliminary data of sectors of industry on automation based on built-in microcomputers of rather large-series equipment. According to literary sources, thousands of varieties of applications of microprocessors and microcomputers are operating in foreign practice.

The indicated materials permit a number of priority fields of SM EVM application to be allocated for the periods 1981-1985 and 1986-1990 with regard to the increasing computer equipment resources and accumulated experience in automation of facilities of different complexity and designation.

They include:

transport—control of switching stations on railroads and cargo handling at seaports, river ports and airports, control of passenger and baggage registration, of the ticket sales system and railroad traffic, control, monitoring and engineering diagnosis of transport facilities and so on;

commerce and material and technical supply--management of warehouse complexes and goods bases, information-monitoring systems of large commercial enterprises;

health--operational physician checking of patients in clinics, diagnostic systems, automated management of medical histories and control of diagnostic and therapeutic equipment;

agriculture—control of the production processes of large animal husbandry and poultry-breeding complexes, combifeed production, greenhouses, enterprises for afterharvest processing and storage of grain, cotton, sugar beets and other crops, management of water distribution networks and information systems of the agrochemical service;

training--occupational and retraining of personnel (simulators, automated classrooms and examination modules and reference systems);

environmental protection--automated systems for monitoring the state of the atmosphere and reservoirs.

Moreover, a number of effective trends in use of SM EVM will achieve significant development in previously adopted (traditional) fields of application (ASU TP, SAPR and SANE): in machine building--control of complexly mechanized sections (machine tools with ChPU [Numerical program control] and robots), machining and

automatic lines, galvanic production, product quality control benches, preparation of programs for machine tools and sections with ChPU and so on; in the food industry--control of production processes at creameries, slaughterhouses, locker plants, canning plants, mills and elevators and confectioners; in construction-extensive use of methods and hardware for automation of design in housing, civil, industrial and highway construction; in prospecting and field geophysics--automation of processing information flows at field stations and at regional centers; in development of local and distributed computer networks (of different classes), preparation of information and remote data processing with organization and development of collective use of computer equipment.

The experience of design and use of simple and complex control and information computer systems, on the one hand, and analysis of the planned trends in use of computer equipment, on the other hand, now make it possible to formulate a rather well-founded scientific and technical concept of small computer development in the country. The concept developed on this basis, which corresponds to the real, specific needs of the national economy and available material resources, is free of copying foreign prototypes and relies entirely on domestic scientific potential.

(This of course does not mean that foreign experience is not studied and not analyzed).

The most important feature of this concept, as already indicated is developing methods of providing the greatest adaptability of hardware to problems of specific users from the position of minimization of expenditures with maximum efficiency of the equipment used.

The main contradiction which must be overcome with extensive introduction of control computer complexes is retaining the advantages of mass production (production of a limited set of devices and modules) with simultaneous fulfillment of the requirements of different users, i.e., provision of economy of funds and time in development of specific control systems.

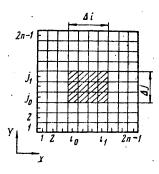

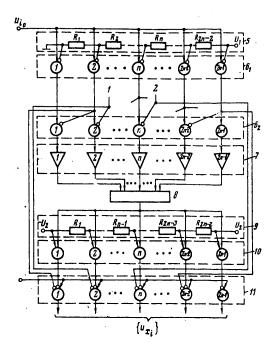

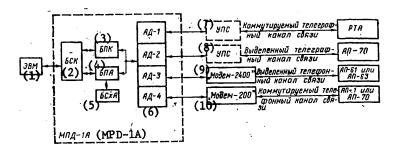

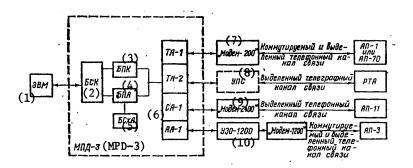

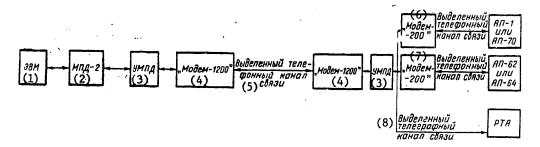

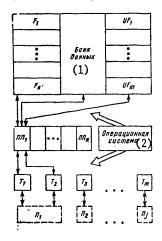

The indicated contradiction within the SM EVM is solved both by increasing the technical level of the models of all devices themselves contained in the SM EVM and in improving their basic nomenclature and technology of combination of hardware and software in developing specific configurations of control computer complexes (UVK).